컴퓨터 아키텍처 1~4장 연습문제 정답과 풀이(한빛아카테미, 우종정 지음)

답지 없이 직접 풀어본거라 틀린 답이 있을 수 있습니다.

잘못된 내용을 발견했을 때 덧글로 의견을 주시면 감사하겠습니다.

1장

1) 4

2) 3 - 입력, 처리, 저장, 출력

3) 2 - 캐시 메모리는 필요에 의해 만든 것이며 필수요소는 아니다.

4) 4

5) 4 - 사우스브리지는 PCI 버스 관리와 연관되어 있다.

6) 1

7) 2 - 보조기억장치에 대한 설명이다.

8) 2

9) 3

10) 4 - 컴파일러의 역할이다.

11) 제어

12) 펌웨어

13) 하드웨어

14) 32가지 - 2^5 만큼 표현이 가능하다

15) 로더

16) 프로그램을 실행할 때마다 해석을 하기 때문이다

17) 부팅

2장

1) 2

2) 1

3) 2 - 58p 참고

4) 3

5) 4

6) 2

7) 3

8) 3

9) 1

10) 3 - 처리율은 단위시간에 처리된 프로그램 수를 의미한다.

11) 틀리다. 컴퓨터 성능을 결정하는 명령어 개수, 평균 CPI, 클록 사이클 시간(클럭 속도와 역수 관계)는 서로 충돌하는 관계이기 때문에 한 요소가 독립적으로 성능을 결정할 수 없다.

12) 폰노이만 병목

13) 폰노이만 아키텍처는 데이터 메모리와 프로그램 메모리를 구분하지 않고 하나의 버스를 사용한다. 이때 발생하는 버스 점유 문제를 해결하기 위해 하버드 아키텍처는 메모리를 2개로 분리하고 CPU의 제어장치와 연산장치를 별도의 버스로 연결해 명령어와 데이터를 병렬로 인출한다.

14) 약 1.05배

15) 덧셈 개선 방법이 약 1.032배 더 좋다.

3장

1) 2

2) 4

3) 1

4) 3

5) 3

6) 2

7) 4

8) 4 - 가변 길이 명령어에 대한 설명이다

9) 1 - 1은 연산, 나머지는 제어 명령어

10) 5

11) PC

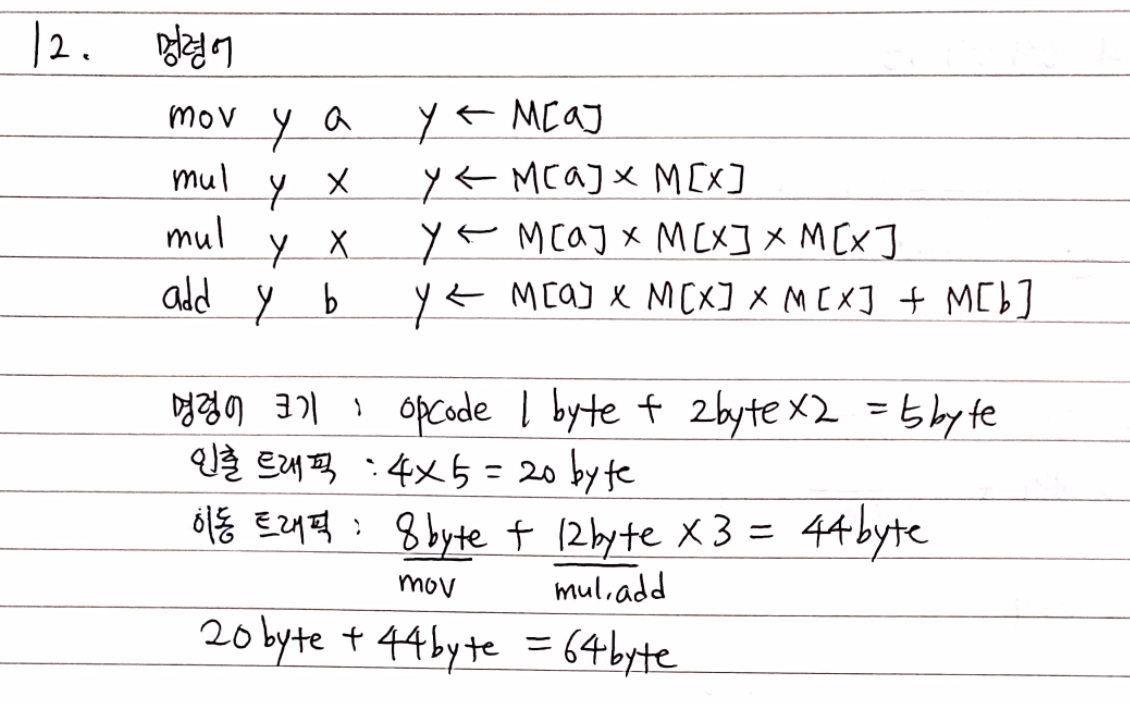

12) 64byte

13) Stack 구조가 아니기 때문에 복귀 주소 관리가 어렵다. 프로시저를 중첩 호출하거나 재진입 가능한 프로시저를 호출할 수 없다.

14) ISA

15) 적절성 - 확장성이 없기 때문이다

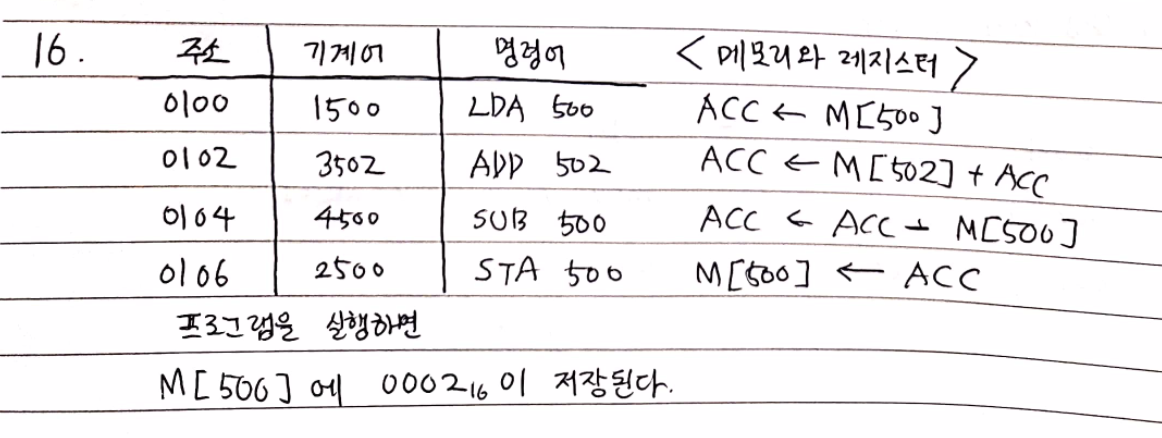

16) 4500은 SUB 500, 2500은 STA 500에 대응된다.

프로그램을 실행하고 나면 메모리 500번지에 0002가 저장된다.

17) MAR ← PC; MBR ← M[MAR]; IR ← MBR; PC ← PC + 4

4장

1) 3

2) 1

3) 2

4) 2

5) 1

6) 3

7) 4

8) 묵시 - 스택에서 pop 연산으로 데이터를 꺼내므로 피연산자를 명시할 필요가 없다.

9) 틀리다. RISC에 대한 설명이다.

10) 피연산자 필드가 짧아지면 명령어 주소가 짧아진다. 명령어의 길이가 곧 명령어 인출 트래픽을 결정하기 때문에 길이가 짧을수록 폰노이만 병목이 줄어든다. 오늘날 컴퓨터는 범용 레지스터 컴퓨터 방식을 사용해 피연산자 필드를 짧게 한다.

11) 단순하지만 실행 시간이 짧은 소수의 명령어로 명령어 집합을 구성한다.

12) 데이터 경로를 단순하게 설계하기 위함이다.

13) 아키텍처가 명시할 수 있는 데이터의 최소 단위이다. 비트 단위를 주소 해상도를 사용할 경우 명령어의 길이가 8의 배수가 아니기에 메모리 정렬이 되지 않는다. 이로인해 명령어의 주소를 명시하기 위해 더 많은 비트를 사용해야 한다. 그리고 명령어가 비트 경계에서도 시작될 수 있어서 인출을 위해 한 번 이상 메모리에 접근해야 할 수 있다. (관련된 내용은 블로그 다른 글의 메모리 정렬 부분을 보면 된다)

14) 자주 사용하는 소수의 데이터에 빨리 접근함으로써 높은 효율과 성능을 보이기에 많이 사용되고 있다. 레지스터 주소가 짧아서 피연산자 필드가 짧아지고 데이터 접근 속도로 빠르다.

15) 빅엔디안 : 1234 리틀 엔디안 : 3412

16) 55byte

실행되는 명령어를 나열하면 아래와 같다.

* 인출 트래픽

load, store -> 명령어당 4byte (opcode 1byte + 레지스터 4비트 + 피연산자 2바이트로 3.5바이트지만 최소 단위가 바이트이므로 4바이트로 간주한다)

add, mul -> 명령어당 3byte (opcode 1byte + 레지스터 12비트로 2.5바이트지만 최소 단위가 최소 단위가 바이트이므로 3바이트로 간주한다)

4byte * 5 + 3byte * 5 = 20byte + 15byte = 35byte

* 이동 트래픽

load, store -> 4byte의 데이터가 5번 이동하므로 20byte

add, mul -> 레지스터로 연산하므로 트래픽이 발생하지 않는다.

20 + 35로 총 55byte가 된다

이 글은 집단 지성의 힘으로 수정되고 있습니다 허허..

덧글로 틀린 내용을 제보해주시는 분들이 계신데, 수동으로 보고 있다보니 빠르게 확인을 못할 때가 있습니다.

공부하려고 방문하신 분들, 혹시 모르니 덧글란에 아직 반영되지 않은 최신 댓글이 있는지 한 번 확인해주세요.

최종 수정일 : 2020년 10월 5일

'if (study) > 기본기 수련' 카테고리의 다른 글

| 컴퓨터 아키텍처 5~7장 연습문제 정답과 풀이(한빛아카데미, 우종정 지음) (11) | 2019.10.25 |

|---|---|

| 아키텍처 별 특징과 폰노이만 병목에 발생하는 트래픽 정리 (0) | 2019.10.21 |

| [Java/Kotlin] 빅 엔디안(Big-Endian)과 리틀 엔디안(Little-Endian) 변환 예제 (2) | 2019.10.17 |